Цифрови импулсни броячи - курсова работа

Двупосочен сериен брояч 8

Паралелно брояч сумиране 12

Стойки с паралелна транспорт 12

Концепция за развитие 14

Pulse шейпър 14

Получаване на блоковата схема на брояча 15

Получаване функционална схема на брояча 16

Най-простият единичен-битов импулсни броячи 16

С развитието на електрониката има такъв клас от електронно оборудване, като например цифров. Тази техника е предназначена за формиране, обработка и предаване на електрически импулсни сигнали и токови удари и ток, и да контролира информацията и да го приберете. Цифрови устройства заемат господстващо положение в много области на науката и техниката, поради значително по-ниска консумация на енергия от електрическата мрежа, по-висока точност, по-малко критичност към промени във външните условия, по-голям шум имунитет. Digital оборудване включва устройства като джапанки, регистри, броячи, комбинирани устройства, програмируеми логически интегрални схеми и др.

Digital импулсен брояч - цифров възел, който изпълнява сметка входящите импулси на входа. Counter преброяване резултат е оформена в предварително определено код може да се съхранява и необходимото време. Стойки се основават на тригери, броят на импулси, който броячът може да разчита определя с израза п = 2 п - 1, където п - брой на джапанки и минус един, защото в цифровата техника приет 0. броячите са сумиране на еталонната точка, когато като отидете да се увеличи, както и изваждане - с намаление. Ако м може да се включи по време на работа с сумиране и изваждане напротив, той се нарича обратим.

Като начална състояние на нулево ниво, приет на всички изходи на джапанки (Q1 - Q3) .., т.е. цифров код 000. В този значителен малко е изхода Q3. За да се превърне всички тригерите в нула държавни R входове на джапанки са комбинирани и са снабдени с необходимото ниво на напрежение (т.е.. Е. Pulse задейства нулират). В действителност тя е сменена с нова. Входният C получава тактови импулси, които увеличават цифров код с един, т.е., след пристигането на първия импулс от първите флип-флоп ключове 1 (код 001), втори тригер след пристигането на втория импулс преминава в състояние 1, и първата - .. Към 0 .. (код 010), тогава третият и т.н. в резултат на такова устройство може да разчита до 7 (код 111), тъй като 2 3 - 1 = установени елемент 7. При всички изходи на джапанки, се казва, че броячът е пълна. След пристигането на следващия (девети) се нулира и импулсен брояч започва всичко отначало. В графики промяната на състоянието на спусъка може да отнеме време TD. Времето за трети разряд се е утроил. Се увеличава с броя на битовете на закъснението е недостатък на броячи с пореден трансфер, въпреки своята простота, ограничаване използването им в приложения с малък брой битове.

броячи за класификация

Стойки е устройство за преброяване на броя на импулсите получени на входните (команди) и памет за съхранение преброяване резултат и извеждане на този резултат. Основният параметър на брояча разчита модул (контейнер) Ks. Тази стойност е равен на броя на стабилни състояния на тезгяха. При получаване Ks импулсен брояч се нулира. За двоични броячи Ks = 2 М, където М - броя на битовете на брояча.

Други важни характеристики противопоставят Ks са максималната честота Fmax и настройка на профила време tust които характеризират тезгяха производителност.

Tust - продължителност на преходно процеса на преминаване към ново състояние на брояча: = tust MTTR, където m - броят на битовете, а TTR - с часовников спусъка.

Fmax - максималната честота на входните импулси, при която не се среща пулс загуба.

Според вида на операцията:

Броячът сумиране на пристигането на всеки импулсен вход се увеличава с един броене резултат на умалител - понижавания; в реверсивни броячи може да се появи като сумиране и изваждане.

Структурна организация:

В последователно брояч вход импулс се прилага само на първото влизане цифри, входовете на всяка следваща освобождаване изходен импулс се прилага преди тя изпълнява.

Успоредно с пристигането на следващия брояч броим ключа импулс задейства прехода към ново състояние се извършва едновременно.

Сериен паралелна схема включва както на предишното изпълнение.

За промените на състоянието:

- с естествения ред на сметката;

- с произволна процедура за броене.

Modulo сметка:

Модул двоичен брояч брои Kc = 2, и не-двоичен брояч преброяване модул Kc = 2m, където m - брой битове на брояча.

Кумулативна последователно брояч

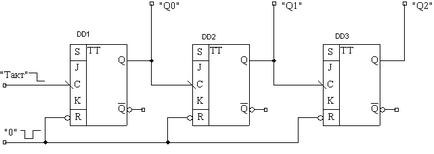

Фиг.1. Обобщавайки поредна 3 битов брояч.

Тригери на тезгяха, предизвикана от падащ фронт на импулса отчитане. Вход ранг старши брояч, свързан с директен (Q) Jr. съседен разряд. Диаграмата на времето на работа на брояча е показано на фигура 2. В началния момента състоянието на всички джапанки са логика 0, съответно, върху тяхната преки изходи логика 0. Това се постига чрез кратко логика 0 прилага за монтаж асинхронни входа на джапанки в логиката 0. Общото състояние на брояча може да се опише чрез двоично число (000). По време на настройка на профила на асинхронни входове на джапанки в логиката 1 се поддържа от логика 1. След пристигането на задната 0 разряд край на първия импулс е включен в обратна състояние - логика 1. На входа на разряд-1 се оказа нарастващ фронт броене пулса. Броячът (001). След като се към входа на задния ръб на втория брояч на импулси разряд 0 е включен в противоположното състояние на - логика 0 на вход 1 се появява освободи централния ръб брой импулси, които се превключва от една-малко в логиката 1. Общото състояние брояч - (010). Следващата попадащи ръба на 0-входа на изпълнението се инсталира в логиката 1 (011) и т.н. По този начин, на гишето се натрупва броя на входните импулси, получени при неговото въвеждане. В получаването на 8 импулса на входа брояч се нулира (000), а след това се брои ставка (KSCH) на брояча е равна на 8.

Фиг. 2. Времедиаграма последователно сумиращо.

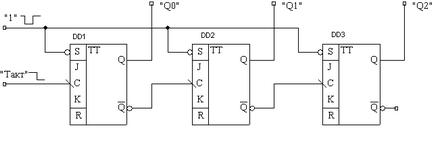

Изваждайки сериен тезгяха

Тригери на тезгяха, предизвикана от падане край. За изпълнение на изваждане операции MSB брои вход, свързан към изхода на обратна съседната LSB. Предварително зададената задейства държавната логика 1 (111). Действието на този брояч показва времето диаграма на фиг. 4.

Фиг. 1 Последователно надолу брояч

Фиг. 2 времедиаграма последователно изваждане брояч

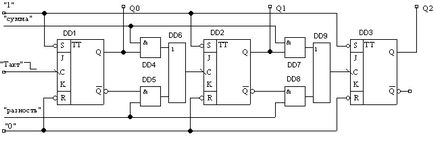

Двупосочен сериен брояч

За изпълнение броячът е необходимо да се съчетават функциите на тезгяха сумиране и надолу брояч функции. Веригата на електромера, показан на фиг. 5. За контрол на режима на сигнали са сметки "сума" и "разлика". За режим сумиране "сума" логика 1 = "0" -kratkovremenny логика 0; "Разлика" = логика 0, а "1" логика 0 -kratkovremenny. DD4.3 на елементи DD4.1 и се оставя храна към входовете часовник на тригерите DD1.2, DD2.1 чрез елементи DD5.1 и DD5.2 директни изходните сигнали от джапанки DD1.1, DD1.2 съответно. DD4.2 елементите и DD4.4 затворен в техните изходи логика 0 присъства, така че ефектът на изхода на обратен не засяга броене спусъка вход DD1.2 на, DD2.1. По този начин, операцията на сумиране се реализира. За изпълнение на операцията по изваждане на входа на "сума" логиката 0 се подава към входа на "разлика" логика 1. DD4.2 елементи, DD4.4 оставя да протече при входовете на елементи DD5.1, DD5.2, и съответно да разчитат входове на тригерите DD1.2, DD2.1 сигнали от изходите на обратни джапанки DD1.1, DD1.2. DD4.1 елементи, DD4.3 затворен и сигнали от директен изхода на тригерите DD1.1, DD1.2 не засяга броене входовете на тригерите DD1.2, DD2.1. По този начин, изваждане се реализира.

Фиг. 3 Сериен заден 3-битов брояч

За изпълнение на тези броячи могат да използват и тригери, основаващи се на нарастващия фронт на импулсите за количество. След това, когато сумиране на входа брой на MSB е необходимо да се сигнализира с прилежаща обърнат изхода LSB и чрез изваждане на обратното - да се присъедини към входа брой, с директен достъп.

Недостатъкът на последователно брояч - чрез увеличаване увеличава дълбочината на битовете пропорционално на инсталацията (tust) на брояча. Предимството е лекотата на изпълнението.

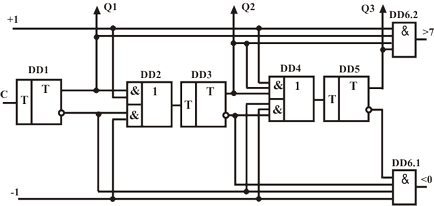

Фиг. 3 - надолу брояч

За преброяване импулси са предвидени два входа, "1" - да се увеличи, "-1" - чрез редукция. Съответният вход (1 или -1) е свързан към входния В. Това може да стане схемата ИЛИ ако vlepit преди първия тригер (елемент изхода към входа на първия тригер, входове - гумите на 1 и -1). Непонятно отпадъци между тригери (DD2 и DD4) се нарича И-ИЛИ. Този елемент се състои от две и порти и един или порта комбинирани в един корпус. На първо място, на входните сигнали на този елемент логично умножават, а след това в резултат на логическата сума.

Броят на входа на И-НОР съответства на броя на освобождаване, т.е., ако третата цифра, трите входа, четвърто -.... И т.н. четири логика схема е превключвател две позиции, управляем директно или обърнати изход на предходната тригер. Когато дневника. 1 да насочи изход брояч брои импулсите от автобуса "1" (ако, разбира се, хранени), с дневника. 1-обратен изход - с "-1" гума. Елементи и (DD6.1 и DD6.2) образуват трансфер сигнали. На изхода 7> сигнал се генерира в код 111 (номер 7) и присъствието на импулс на линия 1, изходът п - 1, където п - брой на джапанки и минус едно, защото в цифрова технология се приемат като произхода 0. броячите са обобщени, когато законопроектът отива да се увеличи, както и изваждане - с намаление. Ако м може да се включи по време на работа с сумиране и изваждане напротив, той се нарича обратим.

Списък на използваната литература

Наръчник "интегрални схеми" BV Tarabrin, LF Лунин, Ю.Н. Смирнов и др. Радио и съобщенията, 1984 София.

VL Шило "Популярни цифрови схеми", радио и съобщенията, София 1987.

AS Partin, VG Борисов "Въведение в цифровите технологии," Радио и съобщенията, София 1987.

BI Goroshkov "Елементи на електронните устройства," Радио и съобщенията, София 1988.

www.qrz.ru материали на сайта са използвани също и електронния "Наръчник на цифрови логически чипове TTL, STTL, видове ECL, част 1".